高速串行总线的物理层一致性测试漫谈

发布时间: 2018-05-05 12:10:16 浏览数:

前言:物理层的一致性测试作为近10多年来示波器主要的用途之一,一直是产业界常提到的名词之一。本文尝试将物理层一致性测试的含义,要素与目的及未来发展趋势做一个简单的探讨和说明。(如无特别说明,本文后续提到的一致性测试均指物理层一致性测试)。

>>> 一致性测试的由来和什么是一致性测试?

英文单词Compliance, 广泛用于各行业,用在电子行业顾名思义就是合乎规范。一致性测试作为产业界工程师们耳熟能详的名词,已经深入人心十几年了。

物理层一致性测试最初发轫于USB2.0标准,由USB-IF协会和业界巨擎Intel公司推广普及。由于采用USB2.0标准的主机(Host)及设备(Device)和集线器(Hub)数量暴增,需要解决各设备之间的物理层和协议层的兼容性和分歧,因此制定了一个统一的标准化的衡量方法来评估各设备的信号质量。一致性测试类似黑盒测试,通常只关注设备外部接口处的信号质量。通过协会认可的一致性测试,可以打上对应的Logo。今天一致性测试已经广泛被各大标准和协议会组织采纳,比如HDMI,DisplayPort,USB3.x,SATA/SAS,PCIExpress,ThunderBolt等。

业界另外一大组织IEEE相应地后来在10/100/1000BaseT的测试上也引入了一致性测试的概念用于评估各设备的信号质量。事实上无论如何沧海桑田,USB2.0和以太网是最成功和经久不衰的两个接口和通讯标准。即使在近几年IEEE发表的最新的200G/400G标准中也定义了类似的测试方法。

那么一致性测试到底是什么呢?

其依据是什么?

在此,笔者给出一个粗浅的定义:业界广泛接受的用同一把尺子来衡量产品的信号质量是否符合标准的测试的统称,其依据就是各个标准和协会组织定义的一致性测试规范CTS(Compliance Test Specification)。通过对产品进行一致性测试,除了了解产品是否符合标准测试规范外,还可以量化信号的各指标距离CTS的裕量。如果裕量充分,则意味着可以对产品进行降成本设计,反之则需要重新设计。对于系统厂家,在快速变化的市场和残酷激烈的竞争面前,降低产品成本是生存的法宝。对于上游芯片厂家而言,基于其芯片的系统经过一致性测试如果可以显示出有非常高的裕量,则可以表明其产品的性能,为其下游客户的产品设计和开发提供了充分的信心和裕量以供进行降成本设计。因此一致性测试对于整个行业而言其重要性不言而明。其依据是什么?

近年来随着数字技术和芯片集成技术的发展,电子电路调试(Debug)在电子产品开发工作中占比越来越小,而一致性测试作为产品最终出货前的一环日益重要也事实成为示波器重要的用途。

>>> 一致性测试的含义或要素

一致性测试如此重要,那么其含义是什么或者说前面给出的定义同一把尺子包含哪些要素?

1. 统一的标准的测试信号

这个统一的标准的测试信号,英文名称是CompliancePattern。从USB2.0开始Intel专门针对PC系统开发了一个软件发包工具(USBHSETTool)发出各种信号,比如测试眼图的TestPacket等。发展到今天支持USB3.x标准的被测设备在上电后发出IN包如果未检测到ACK包,即进入Compliance测试模式,发出各种CompliancePattern. PCIExpress标准的原理类似。也有特例比如显示技术HDMI就不太一样,Sink设备一般无高速信号回传给源端,因此需要采用外接EDIDEmulator来欺骗源端设备已经外接某一格式的Sink设备,源端设备就会开始输出信号。而DisplayPort标准和SATA标准通常需要修改寄存器配置测试码型。有的标准还支持通过外接控制器用软件进行自动化配置测试码型以配合一致性测试,比如Unigraf公司开发的DP测试控制器和Wilder公司开发的Thunderbolt控制器。

为什么会定义统一的测试信号呢?因为采用不同的码型进行测试,得出的测量结果也是不一样的。比如采用0101码型和采用00110011码型,得到的ISI抖动肯定是有差异的。所以为了统一和规范测量,协会和标准组织定义了标准的测试码型。当前最典型的是USB3.1标准定义了多种分别用于不同测试项目的码型:

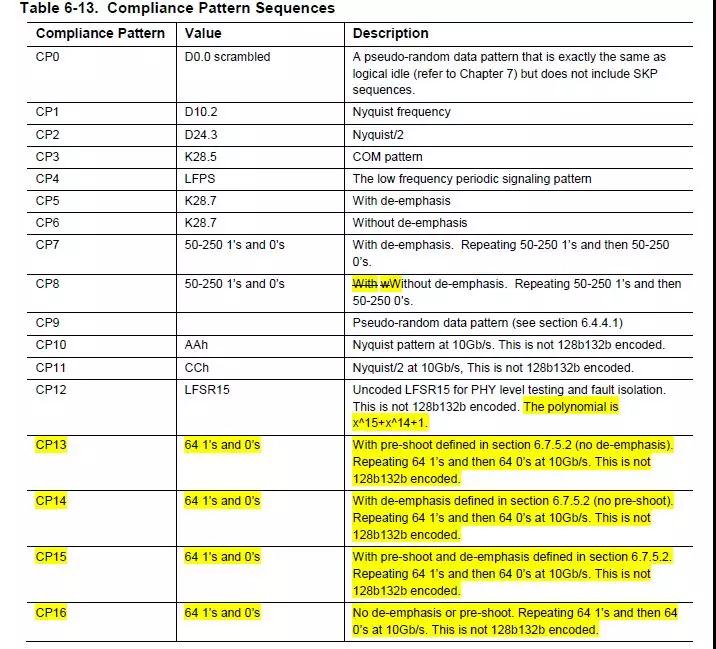

USB3.x测试码型表

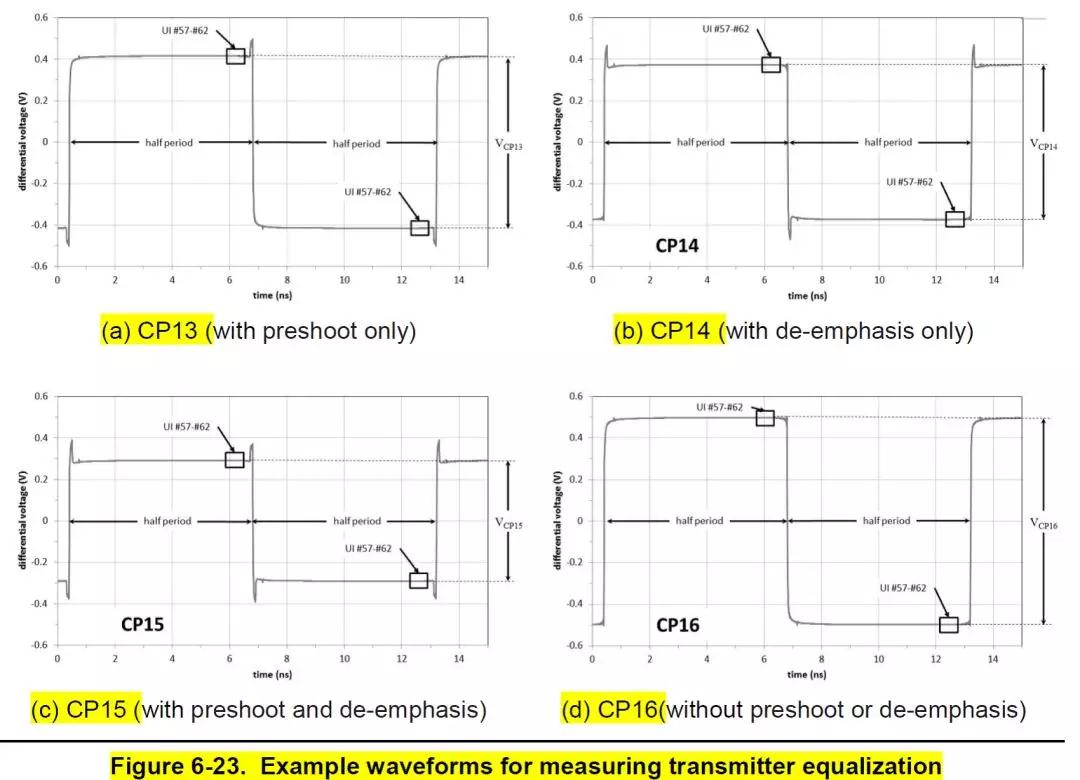

以上黄色标注的码型CP13-CP16,是USB3.1规范里新增加用于测试发送端预/去加重或均衡的码型:

USB3.1 CP13-CP16码型说明图

2. 标准的连接方式,通常为夹具和电缆组合

另外为了统一测试环境,协会和标准组织还定义了标准的连接方式,通常采用协会或第三方公司开发的标准夹具和电缆。夹具和电缆通常都是为了方便测试连接而引入的部件,必然会引入测试误差,降低系统的测试裕量。因此在一致性测试过程中,必须要求采用相同的测试工具以标准化测量避免测试差异。

在当下主流的各种标准中,除了USB3.x和PCIE夹具依然主要是由Intel主导的USB-IF和PCI-Sig协会组织提供外,其它各种标准的夹具Wilder公司均可提供。

在测试连接上,HDMI标准由于最初需要接入3对Data,1对CLK同时进行测试,采用了夹具 连接SMA探头再连接到示波器上进行测试,以实现一次完成所有差分项目的测试。

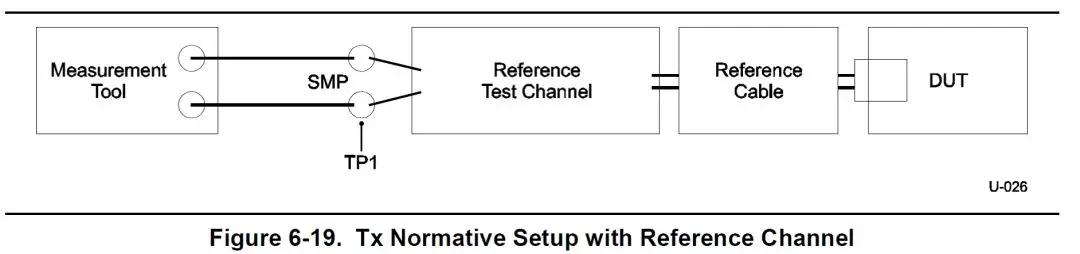

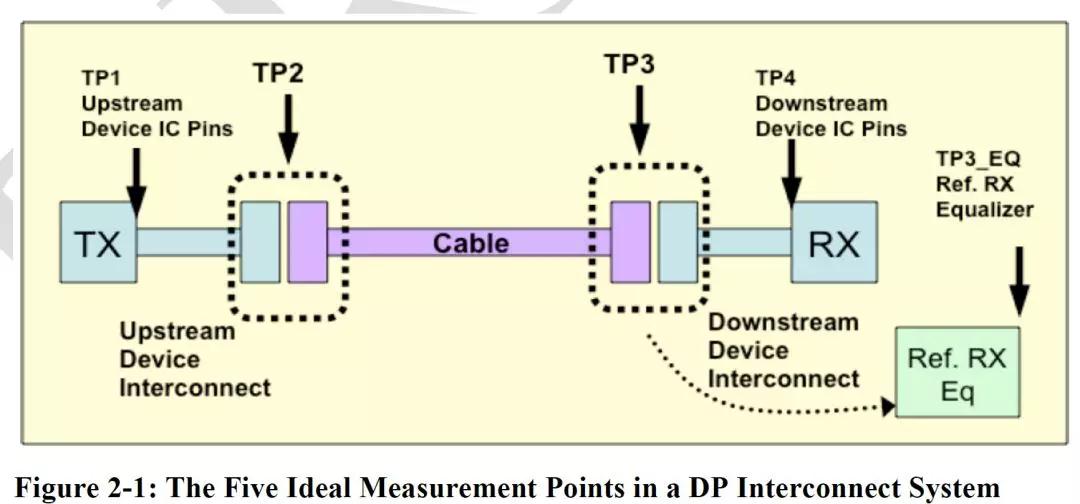

在标准和规范定义中,一般会定义若干测试点,比如USB2.0规范里定义了TP1,TP2,TP3,TP4.TP2是典型的Host测试点位置,而TP3则是典型的Device设备的测试点位置。不同的标准定义的测试点含义不同,比如到USB3.x标准则主要定义了TP1--发送端测试的远端测试点,而TP0通常指发送端近端测试点仅在示波器的测试软件里作为Informative测试:

USB3.x测试方法拓扑说明图

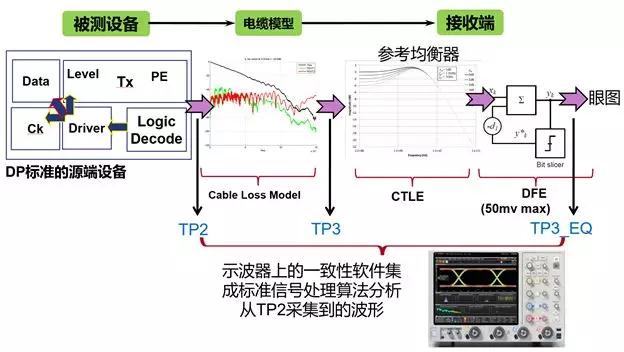

近两年在信号速率持续推高到5Gbps以上后,通常在测试点上还引入了TPxEQ测试点,比如DP1.4标准中,定义的测试点就是TP3_EQ,这个测试点通常表征的是接收系统里经过均衡算法后的测试点,而实际测试中通常是无法探测得到的,需要在示波器上的一致性测试软件里模拟接收端的均衡算法:

DP1.4测试点定义和拓扑图

3. 标准的测试算法和流程

被测设备发出标准的测试码型并通过夹具和电缆连接到示波器后,示波器作为接收端,模拟芯片接收端的信号处理方法对信号进行测试和分析,除了常规的针对信号的电气特性参数测量外,通常还要执行眼图和抖动分析。本文提到的标准测试算法在早年主要指时钟恢复和眼图与抖动分析方法,比较简单。近几年在高速串行总线系统普遍引入和嵌入和均衡等技术,信号分析算法程度大大提高。

典型的外部接口标准如USB3.x/HDMI2.x/DP1.4均需要测试远端眼图,在实际连接中采用的是在被测设备近端即发送端用夹具拾取信号然后嵌入标准提供的电缆参数模型模拟真实的传输电缆,此有损电缆参数模型给信号带来很大的衰减,在接收端必须采用均衡算法(CTLE/FFE+DFE)恢复信号。示波器上运行的一致性测试软件则会完全嵌入接收端的标准均衡算法恢复信号然后进行各参数分析和眼图与抖动测试。以DP1.4标准为例:

DP1.4测试原理框图

可见,在今天的高速信号测试中,一致性测试软件的地位和作用日益重要。一致性测试软件除了执行标准的测试算法进行分析并给出测试结果外,有时还可以进行一些配置的改变以进行调试性测试,即修改一些测试配置参数和选项,称之为Debug Mode。

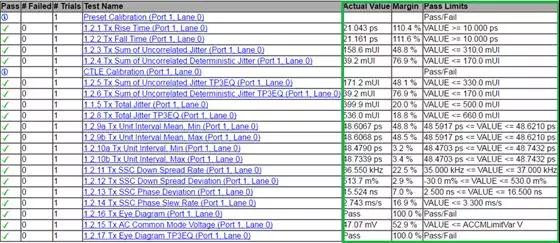

一致性测试软件在测试完毕后会将所有测试结果整理输出成为报告,在报告中会专门标注每个测试项目的裕量水平,比如下表所示Keysight Thunderbolt N6470B测试报告,绿色方框内分三列显示测量值,裕量及Pass/Fail判断:

Thunderbolt一致性测试软件结果报告

事实上,今天Server,PC和笔记本行业的很多接口标准比如PCIE,SATA,USB3.x等,业界主导公司Intel还开发了专门的测试软件Sigtest可以进行数据后分析。在Sigtest软件里会针对不同的标准不同的测试点定义一些不同的测试脚本文件(在Sigtest安装文件夹的Template文件夹里)。标准的一致性测试软件中通常也可以调用Sigtest程序里的DLL(动态链接库)文件执行此行业内主导公司的标准算法测试。

囿于篇幅和标准的多样性及水平有限,本文这里就不再对测试算法做深入探讨和描述。

4. 影响一致性测试精度的因素

前面我们描述了一致性测试的含义与本质,一致性测试到底在追求什么?归根结底是裕量(Margin)。其本质或者最终的动机就是降成本。

对于系统厂家而言,在产品设计完成后如果经过一致性测试,发现信号质量距离CTS规范规定的要求有较大的裕量,那就意味着可以对产品进行降成本设计,比如可以减少电容,或者采用更廉价的连接器乃至降低PCB层数等,所有的每一个看起来很小的降成本考虑,在规模化的大批量生产时都会被放大,从而带来可观的经济效益。当然降成本设计也不是无底线的,底线就是CTS,所以业界有很多厂家有时会反复对产品进行设计和测试以找到最终的平衡点,示波器在这个过程中就在扮演重要的角色。对于芯片或产业链上游厂家而言,在产品设计完成后也需要进行参考设计并做一致性测试验证以提交报告给下游厂家,以证明其产品的高品质和大裕量并给予其客户足够的信心以进行降成本设计。

测试测量过程必然会带来误差,那么如何将误差降到最小或得到最高的Margin?除了我们前面讨论的3点,确保进行正确的一致性测试外,就必须要从仪器设备方面考虑。

首先是要选择恰当的示波器,示波器的一些指标如带宽,采样率,底噪和抖动等均会影响一致性测试的裕量。关于带宽是很多人都比较耳熟能详的指标,经常提到的选择正弦波3-5被带宽以及方波9倍频率的带宽等,针对一般的高速串行总线数据(NRZ编码)过去主要采用一种速算法:信号频率/2*5,比如5GBps的NRZ信号,基波频率为2.5GHz,采用2.5GHz*5=12.5GHz以上即可。

另外更加准确的是根据被测信号的上升沿时间计算带宽,通常为20%-80%上升沿时间,信号频率Bw=0.4/Tr,推荐的示波器带宽再乘以1.4~1.8左右的系数即可。带宽不能满足测试要求会直接削减信号的幅度从而直接影响到眼高幅度和上升沿的准确测试。

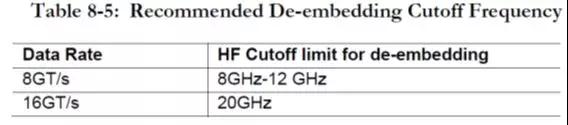

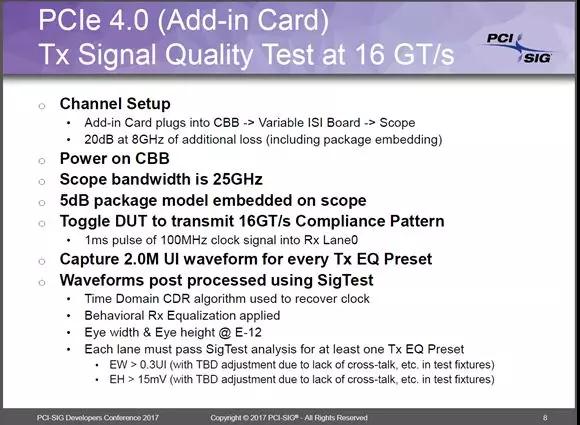

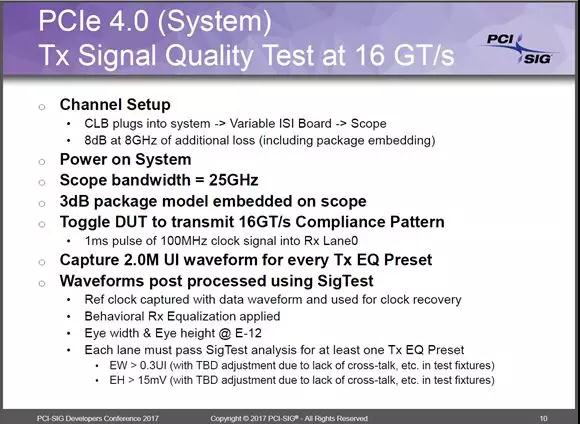

近年随着技术的发展去嵌和均衡的引入,这一规则也在改变。比如针对PCIE4.0 16.0Gbps,为了防止去嵌过度放大仪器的本底噪声,因此在PCIE4.0规范里给出的推荐的CTLE和去嵌的截止带宽频率是20GHz:

PCIE4.0规范推荐的去嵌截止频率点

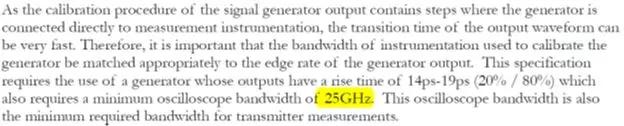

另一方面针对RX测试时的信号源校准为了确保精确校准误码仪输出的信号的边沿,在规范里推荐了25GHz带宽的示波器进行测试:

两者兼顾,在CEM测试中针对PCIE4.0推荐的带宽就是25GHz:

PCIE4.0 Compliance Updates关于一致性测试带宽说明

采样率是示波器另外一个重要指标。对今天的数字实时示波器而言,采样率必须是示波器带宽的2.5倍才能保证将信号准确还原。虽然奈奎斯特采样定理指出2倍采样可将信号还原,但是奈奎斯特定理针对的信号是正弦波,而今天的被测信号多为高速数字信号。

另外两个比较明显的影响比较大的指标是示波器的本底噪声和抖动。示波器的固有抖动对眼图测试时的影响也是类似的,必然会增加抖动类相关项目测试的误差。由于均衡和去嵌均在信号垂直幅度方向对信号进行补偿,叠加在固有抖动上的作用和影响需要进行严格的数学运算定量分析。对于还需要采用探头进行测试的HDMI接口,探头接入信号时由于其固有的衰减特性在对信号衰减后才会进入示波器的前端和ADC采样,示波器会对信号再进行放大同时会放大本底噪声,因此探头的衰减倍数也是影响一致性测试精度和裕量的因素之一。关于示波器的本底噪声对眼图测试的影响可参见参考文献《浅论示波器的低本底噪声对高速眼图测试的意义》。

>>> 一致性测试的发展趋势

最后再来谈谈一致性测试的发展趋势。作为产品出货前的重要环节,一致性测试既然在今天的各种产品研发和制造中扮演着如此重要的作用,必然会带来巨大的工作量和负担。因此从最初的几百MBps级的USB2.0和Ethernet 10/100/1000 BaseT到今天的几十Gbps的高速串行数据标准,一直在朝向更加简单,更加标准化,更加自动化的方向发展,最终的宗旨和目的是为了降低测试复杂程度,提高生产效率。

更加简单,主要体现在测试码型的输出上。如前文讨论,从最初的需要专门的发包软件或者改寄存器输出测试信号到今天的内置BIST(Built in Self-Test Pattern)测试码型,目前在PCIEXpress和USB3.x上均已实现。在DisplayPort和Thunderbolt两种标准上,则有第三方开发的专门的测试码型控制器,比如Unigraf提供的DP控制器和Wilder公司提供的Thunderbolt控制器。

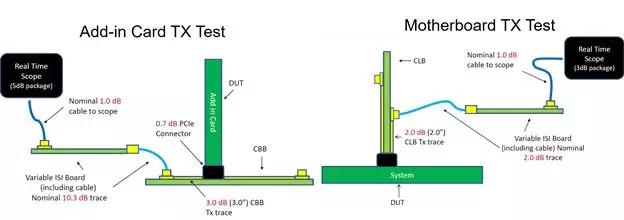

更加标准化,体现在测试连接的定义上。比如在USB3.0测试方法的定义上,最初定义采用通过协会认可的实物电缆来模拟远端测试点,但是后来由于实物电缆依然存在差异,因此后来采用S参数模型替代实物电缆,如此完全消除了不同连接环境的差异。这一方法今天在HDMI2.0/DP1.4也得到了应用。在PCIE4.0规范里,也采用了类似的方法,不过不是软件S参数模型而是采用由协会提供的一块硬件的ISI夹具板来模拟整个链路,以CEM Add-in Card TX测试为例,专门设计了ISI夹具板用于模拟额外的标准20dB@8GHz损耗:

PCIE4.0 CEM测试原理框图

PCIE4.0 CEM ISI夹具板

这一硬件ISI夹具由PCI-Sig协会组织出售,具有唯一性和标准性。未来是否会采用软件的S参数模型方法去实现,当然也不排除这种可能性。

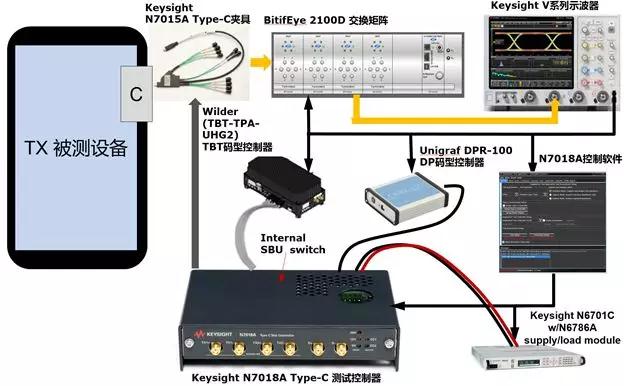

最后一个趋势是,测试自动化的要求日益凸显。由于多种标准和接口纷繁复杂,给消费者带来许多使用上的困扰,同时也加剧了研发设计和测试的复杂性。因此产业界正在努力推广采用唯一的Type-C接口,USB,DP,HDMI,Thunderbolt等标准均支持这一接口。Keysight公司洞悉这一趋势推出了全自动化的针对Type-C接口的测试方案:

Keysight Type-C接口测试方案框图

总结:

本文讨论了发送端物理层一致性测试的含义,要素及目标和趋势,囿于篇幅无法就许多细节进行详细说明。除了发送端之外,近几年接收端的一致性测试随着信号速率的飞速提升也开始成为各种标准必须考虑的测试内容,请留意更多论述和分享。

参考文献:

1.USB3.1 Spec and USB3.1 ECN CTLE, USB-IF

2. PHY CTS v1.4 source DRAFT_rev1, VESA org

3.01_06_PCIE Compliance Updates, PCI-Sig

4. NCB-PCI_Express_Base_4.0r1.0_September-27-2017-c, PCI-Sig

5.Keysight DP Test Solution

6.Keysight Type-C Solution

7. 浅论示波器的低本底噪声对高速眼图测试的意义,Keysight Technologies